4月份登录嘉立创下单助手的时候突然送了张券,正好那段时间还在折腾7035的DDR,想着干脆自己重新画一块试试,最开始想7035扩展为两片DDR,但考虑到7035片子贵的离谱,便准备把主控换成7020,虽然7020已经有开源了,但7020有两个版本,clg400和clg484,484相比400多了一个HP bank,更多的IO意味着可以驱动更多adda。484相比400,多了2个HP bank,满打满算多了25*2对差分,可以多驱动两个16位高速lvds ADDA。

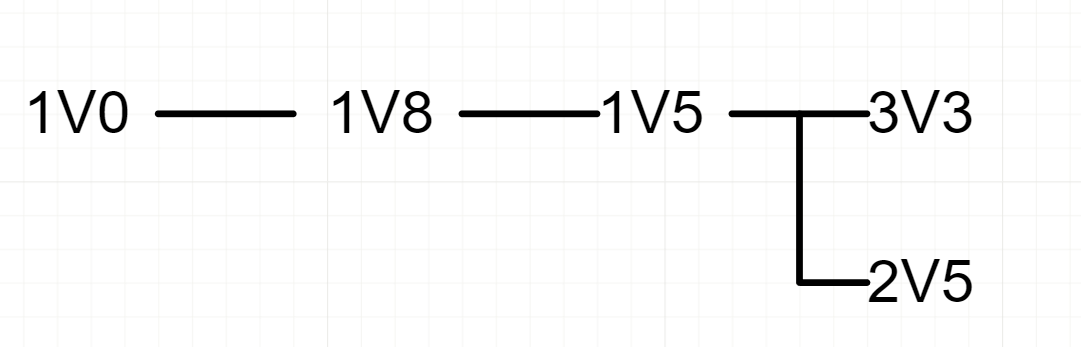

一、电源

7020对电源要求不高,因为之前买了很多TPS82130,加上这个模块对布线要求不高,便很愉快的选用他。

上电顺序,先满足PS的INT,接着辅助电源AUX,然后IO BANK用的3V3和2V5。

其中bank13和bank33用2v5和1v8是为了满足LVDS收发条件,参考【硬件】两张图彻底说明白xilinx7系列HP 与HR的LVDS供电要求(避免踩坑)_hr lvds-CSDN博客,这张图在Xilinx手册里也有。

剩下的BANK34和35就绑了3v3用作pmod。

其他电源设置参考了正点原子和RIGUKE的7020。

二、DDR

DDR用的单片镁光MT41K256,老朋友。

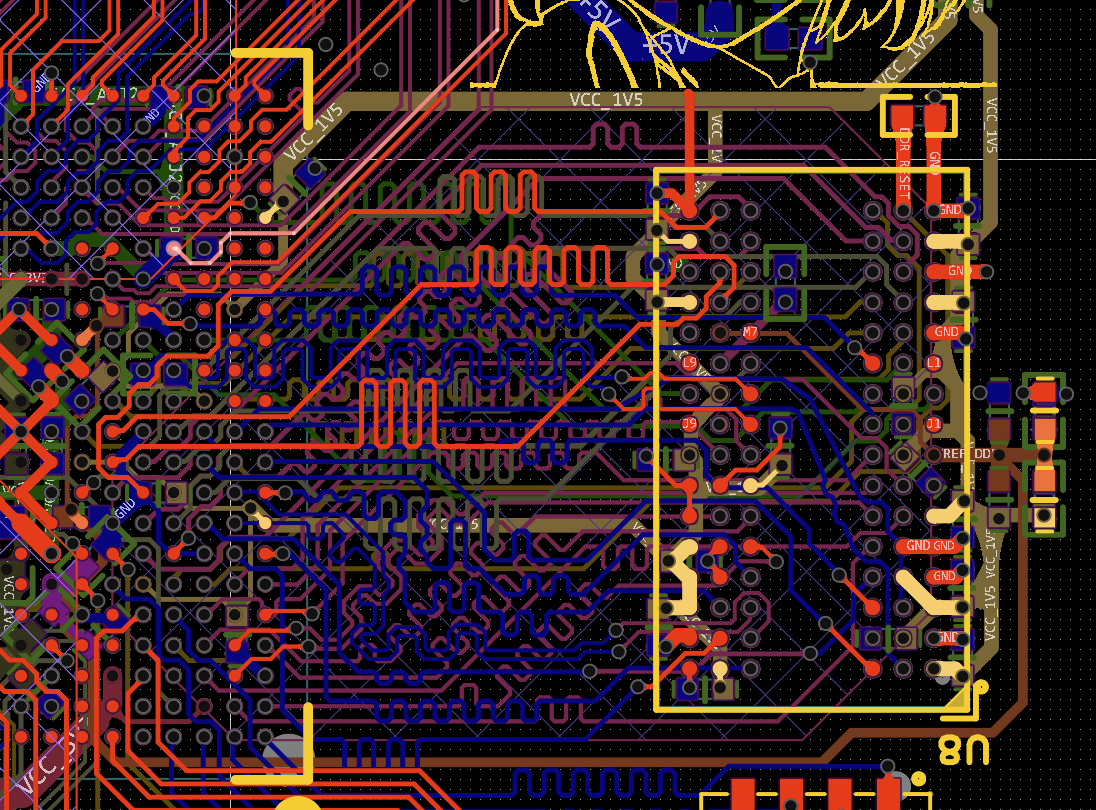

DDR数据按字分组、每组同层等长,地址线不同层、等长,参考了嘉立创的教程https://www.bilibili.com/video/BV1gyNgeHEWN

实际走线还有很大优化空间。

三、IO引出

BANK13和BANK33的IO全引出到一个120pin连接器,共48对差分,未等长,留到底板做调整。

小技巧先不绑引脚,把所有能顶层走的线线拉出来,然后再打过孔拉里面的点。

四、串口JTAG外设

照抄了ZYNQ7020核心板及各种射频模块 - 立创开源硬件平台

五、总结

第一次试画了多层核心板,初心是用掉这张券,实际后续调通是件费时间的事,主要难度在于手工smt,很容易埋下小坑